# К573РФ3, К573РФ3А К573РФ3Б, К573РФ31, К573РФ31А, К573РФ31Б, К573РФ32, К573РФ32А, К573РФ32Б, К573РФ33, К573РФ34

Микросхемы представляют собой перепрограммируемое постоянное запоминающее устройство емкостью 64 кбит (4096х16) у К573РФ3, К573РФ3А, К573РФ3Б; емкостью 32 Кбит (2048х16) у К573РФ31, К573РФ31А, К573РФ31Б, К573РФ32А, К573РФ32Б; емкостью 16 Кбит (1024х16) у К573РФ33, К573РФ34, с ультрафиолетовым стиранием и электрической записью информации. Выполнены по п-МОП технологии.

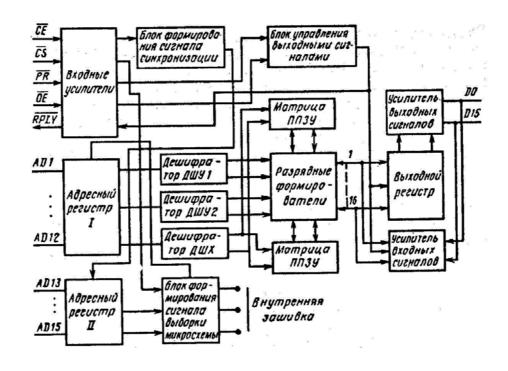

В состав ИС входят входные усилители; адресные регистры, блок формирования сигнала синхронизации; блок формирования сигнала выборки микросхемы; дешифраторы; блок управления выходными сигналами, матрицы ППЗУ, разрядные формирователи, усилители входных и выходных сигналов и выходной регистр. Предназначены для построения блоков памяти микро-ЭВМ. Входы и выходы в ИС совмещены, поэтому передача данных осуществляется в мультиплексном режиме. Три старших разряда используются для программирования кода микросхем, что обеспечивает выборку одной из 8 микросхем на общую магистраль без дополнительного дешифратора. В ИС используются 4 управляющих сигнала: "обмен" (обеспечивает запись адреса в входной регистр; "чтение-программирование" (определяет режим работы); "разрешение чтения" (используется для выдачи считанной информации на общую магистраль при наличии сигнала "обмен"); "ответ" (сопровождает информацию, поступающую из РПЗУ на общую магистраль).

К573РФ3 содержит 140 000 интегральных элементов; К573РФ31, К573РФ32 — 70 000, К573РФ33, К573РФ34 — 40 000. Корпус типа 210Б.24 -1.02. масса не более 5 г.

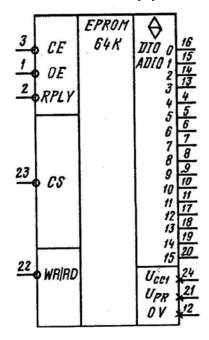

#### Назначение выводов К573РФ3

1 — вход сигнала чтения; 2 — выход сигнала ответа; 3 — вход сигнала синхронизации; 4, 5, 6, 7, 8, 9, 10, 11 — вход (выход) 4, 5, 6, 7, 8, 9, 10, 11 разрядов адреса-данных; 12 — общий; 13, 14, 15, 16 — вход (выход) 3, 2, 1, 0 разрядов адреса-данных; 17, 18, 19, 20 — вход (выход) 12, 13, 14, 15 разрядов адреса-данных; 21 — напряжение питания (Uп $_2$ , Upr); 22 — сигнал записьсчитывание; 23 — сигнал выбора микросхем; 24 — напряжение питания (Uп $_1$ )

Примечание. У К573РФ31 вывод 17 не используется и соединен с выводом 24; у К573РФ32 вывод 17 не используется и соединен с выводом 12; у К573РФ33 выводы 11 и 17 не используются и соединены с выводом 24; у К573РФ34 выводы 11 и 17 не используются и соединены с выводом 12.

## Электрические параметры

$< 800 \; \mathrm{Hc}$

Номинальное напряжение питания:

в режиме чтения:

$\begin{array}{ccc} U\pi_1 & & 5 \ B \pm 5\% \\ U\pi_2 & & 5 \ B \pm 10\% \end{array}$

в режиме программирования информации и кода микросхем:

$5 B \pm 5\%$  $U\pi_1$ Uп<sub>2</sub> (импульсное)  $18 B \pm 5\%$ Выходное напряжение низкого уровня < 0.5 B> 2.4 BВыходное напряжение высокого уровня Ток потребления в режиме программирования < 40 MAДинамический ток потребления < 80 MAВходной ток низкого (высокого) уровня < 1 MKAВремя выборки адреса < 450 HcВремя выборки разрешения: К573РФ3, К573РФ31, К573РФ32 < 400 HcК573РФ3А, К573РФ31А, К573РФ32А < 550 нс

К573РФ3Б, К573РФ31Б, К573РФ32Б

К573РФ33, К573РФ34 < 400 нс

Время сохранения выходной информации

после сигнала чтения

< 100 нс</td>

Время хранения информации

< 15 000 ч</td>

Количество циклов перезаписи

10

Время записи информации

< 50 мс</td>

Время стирания информации

30...60 мин

Время записи информации по одному и тому же адресу 10...150 нс

Параметры УФ - источника:

длина волны 400 нм интегральная доза облучения при энергетической

освещенности 100 Bт\*м<sup>2</sup>

10 Вт\*c\*см<sup>2</sup>

Адресация ячеек:

К573РФ3, К573РФ3А, К573РФ3Б 0...4096 К573РФ31, К573РФ31А, К573РФ31Б 0...2047 К573РФ32, К573РФ32А, К573РФ32Б 2048...4096 К573РФ33 0...1023 К573РФ34 2048...3072 Время программирования 40 с

## Предельно допустимые режимы эксплуатации

Напряжение питания в режиме считывания Un<sub>1</sub> 4,75...5,25 В

Напряжение питания в режиме программирования Uп<sub>2</sub> 18...19,8 В

Напряжение сигнала входной информации:

низкого уровня < |-0,3| В высокого уровня < 5,25 В Значение статического потенциала = 200 В Емкость нагрузки = 60 пФ = 10...+70 °C

#### Рекомендации по применению

Потребителю схемы поставляются с полем высокого уровня. При записи кода микросхемы на вывод 1 подается +5 B; при перезаписи A12 на A0 на вывод 1 подается низкий уровень. Вывод 2 следует подключать через нагрузочный резистор 1,3 кОм  $\pm$  10% к источнику питания  $U\pi_1$ .

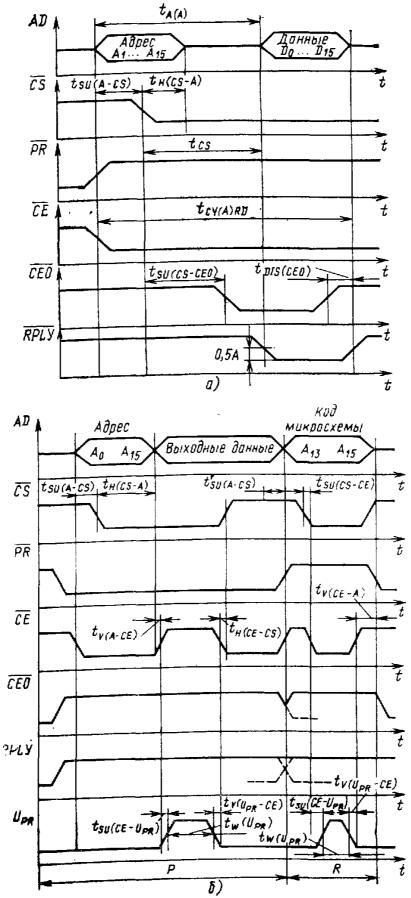

Временные диаграммы работы микросхемы К573РФ3

а — режим считывания; б — режим программирования (P — при программировании информации, R — при программировании кода микросхемы)

Микросхема имеет встроенные средства сопряжения с магистралью по интерфейсу, определенному ГОСТ 26765. 51—86. Кроме того, микросхема имеет встроенное программируемое трехразрядное устройство для записи собственного адреса (номера) микросхемы Амс и схему сравнения для опознавания своего адреса в потоке адресных кодов, поступающих из магистрали.

Микросхема имеет совмещенные адресные и информационные выводы, которыми ее подключают к общей шине «Адрес—Данные> магистрали. Код адреса состоит из двух частей: AD15...AD13 — код адреса микросхемы; AD12...AD1 — код адреса выбираемой ячейки памяти; разряд A0 в адресном коде может иметь произвольное значение

Эти же выводы используются для ввода данных при программировании DI0...DI15 и вывода считываемых данных DO0... DO15. Коды адреса и данных разделены во времени.

Для управления работой микросхемы служат следующие сигналы: СЕ — синхронизация, СЅ — выбор микросхемы, РR — программирование (запись); ОЕ — разрешение выхода (считывание). Названные сигналы являются входными для микросхемы и выполняют следующие функции (в режиме считывания): по сигналу СЕ (соответствует сигналу SYN линии управления) начинается обмен информацией ПЗУ с магистралью, сигнал ОЕ (соответствует сигналу RD) определяет момент передачи данных от ПЗУ в магистраль, сигнал СЅ открывает доступ к микросхеме.

В режиме считывания микросхема формирует сигнал ответа RPLY, который сопровождает выдаваемые в магистраль данные. Состояния сигналов управления в различных режимах работы микросхемы приведены в таблице:

| Сигнал         | Запись адреса<br>А <sub>мс</sub>                              | Запись данных                                                | Считывание                                                   | Хранение   |

|----------------|---------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------|

| CS<br>OE<br>PR | 0                                                             | 0                                                            | 0                                                            | 1          |

| CS             | 0                                                             | 1                                                            | 0                                                            | 1          |

| ŌĒ             | 1                                                             | 1                                                            | 0*                                                           | 1          |

| PR             | 1                                                             | 0                                                            | 1                                                            | 0          |

| UPR, B         | 18*                                                           | 18*                                                          | 5                                                            | 5          |

| ADIO           | $\overline{\mathbf{A}}_{13} \dots \overline{\mathbf{A}}_{15}$ | $\overline{\mathbf{A}}_{1} \dots \overline{\mathbf{A}}_{15}$ | $\overline{A}_1 \dots \overline{A}_{15}$                     | X          |

|                |                                                               | $\overline{\mathrm{DI}}_0 \dots \overline{\mathrm{DI}}_{15}$ | $\overline{\mathrm{DO}}_0 \dots \overline{\mathrm{DO}}_{15}$ | !          |

| ĀN             | 1                                                             | 1                                                            | 0                                                            | 1          |

| tw, мс         | 50                                                            | 50                                                           | 0,45 мкс                                                     | <b> </b> - |

При реализации управления необходимо иметь в виду, что совмещенные адресные и информационные выводы ADIO работают в мультиплексном режиме: вначале на них поступают адресные сигналы, затем выводятся (при чтении) сигналы кода данных. Процесс адресного обращения происходит в следующем порядке. Вначале на входы микросхемы поступает код адреса AD1... AD15 и сигнал CS = O. В микросхеме принятый с адресной шины код AD13...AD15 сравнивается с собственным адресом Aмс и при совпадении с поступлением сигнала синхронизации CE (SYN) код адреса AD1...AD15 записывается во внутренний регистр. Для надежной записи необходимо адресные сигналы сохранять относительно перепада H/L сигнала CE на время  $t_{H(C-A)} = 50$  нс. После этого адресные сигналы снимаются и выводы переходят в Z-состояние в ожидании выдачи данных в магистраль. Считанные из накопителя данные размещаются во внутреннем регистре данных и появляются на выходах по сигналу OE = 0 через время  $t_{A(OE)}$ .

В режиме записи данных при программировании адресное обращение осуществляют аналогично режиму считывания. При поступлении записываемого кода данных сигнал CS принимает состояние лог. 1. Этот режим осуществляют при сигнале PR=0.

Для записи кода Амс необходимо на выводы AD13...AD15 подать сигналы кода A13...A15, а также сигналы управления.

Наличие программируемого адресного устройства и селектора адреса позволяет без дополнительного оборудования объединять до восьми микросхем путем их непосредственного подключения к магистрали. Микросхема совместима по разводке выводов и сигналам с микросхемами КР537РУ11, К1809РУ1, К1809РЕ1, К1801РЕ1, К1801РЕ2, КР588РЕ1, что делает возможным создание универсальных модулей ЗУ на основе стандартного параллельного магистрального интерфейса с объединенной шиной адреса и данных.