Состоит из двух частей, связанных друг с другом только разработчиком/производителем.

КМОП-технология, производитель - "Интеграл", г.Минск (Белоруссия)

![]()

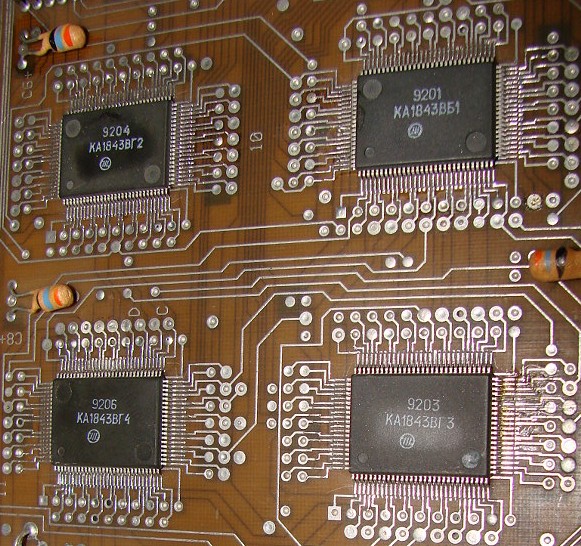

Первая - чипсет для EGA-контроллера (аналоги 82C431...82C434). Справочный лист на них. Применялись в ЕС1849 - отечественной 80286-персоналке.

КА1843ВБ1 - схема синхронизации

КА1843ВГ2 - контроллер электронно-лучевой трубки (EGA)

КА1843ВГ3 - графический контроллер

КА1843ВГ4 - контроллер атрибутов.

Комплект формирует изображения в буферной памяти и управляет отображением на экране видеомонитора алфавитно-цифровой и графической информации с разрешающей способностью 640х200 точек (возможен режим с разрешающей способностью 640х350 точек).

(фото Сергея Фролова)

![]()

Вторая - микропроцессорный комплект - аналог Am293xx, сопроцессоры с командами форматов ЕС и СМ и набор периферии к ним. Применялись, в частности, в ЕС1842.

![]()

(фото с форума Портативное

ретрорадио)

Микросхема К1843ИР1 (позднее она выпускалась в варианте КА1843ИР1) является отечественным аналогом Am29C334. Она представляет собой 4-портовую регистровую память с двусторонним доступом и организацией (64x18) бит: шестьдесят четыре 16-разрядных РОН + 2 паритетных бита. Имеет два порта записи и два порта считывания для данных и четыре 6-битовых адресных порта. Пара адресных портов (один для записи и один для чтения) связана с соответствующей парой портов записи и чтения данных. Многопортовая организация и развитое управление выбора позволяет выполнять два чтения и две записи за один цикл.

Микросхема может быть использована в качестве сверхоперативных

регистров общего назначения в высокопроизводительных системах на

основе комплекта К1843. Разрядность регистров выбрана исходя из расчета

возможности хранения двух байтов вместе с их контрольными разрядами.

Структурная схема БИС включает блок памяти RF емкостью 64x18;

18-разрядные входные магистрали DA, DB; 18-разрядные выходные магистрали VA,

VB портов А и В соответственно, а также магистрали AWA, AWB адресов

записи и магистрали FRA, ARB адресов считывания для портов А и В

соответственно.

Структурная схема БИС включает блок памяти RF емкостью 64x18;

18-разрядные входные магистрали DA, DB; 18-разрядные выходные магистрали VA,

VB портов А и В соответственно, а также магистрали AWA, AWB адресов

записи и магистрали FRA, ARB адресов считывания для портов А и В

соответственно.

При считывании по обоим портам могут использоваться любые адреса,

в том числе и одинаковые. При записи запрещается производить запись по одному

и тому же адресу с обоих портов одновременно. Адресные мультиплексоры

MYXA и MYXB осуществляют раздельное дешифрирование адресов записи и считывания,

что обеспечивает минимальную задержку прохождения кодов адреса в блок памяти.

Выборка адреса записи или адреса считывания осуществляется по сигналам

разрешения записи WEAC для порта А и WEBC для порта В. Кроме того,

для каждого порта имеются входы WEAH, WEBH разрешения записи старших

девяти бит и входы WEAL, WEBL разрешения младших девяти бит,

что фактически обеспечивает доступ отдельно к каждому байту блока памяти.

Выходные регистры RGA и RGB предназначены для приема из блока памяти

18-разрядных кодов и выдачи их на выходные магистрали YA и YB.

Запись информации в регистры RGA, RGB осуществляется по синхросигналам LEA,

LEB. Регистры RGA, RGB управляются уровнем синхросигналов.

При высоком уровне LEA, LEB производится запись информации в регистры RGA,

RGB. При переходе сигналов на входах LEA, LEB из высокого в низкий уровень

происходит "защелкивание" информации в регистрах. Выдача информации

из регистров RGA, RGB на магистрали VA, VB осуществляется по низкому уровню

стробов разрешения выдачи ОЕА, ОЕВ. При высоком уровне этих сигналов

выходные магистрали устанавливаются в третье состояние.

Кроме использования в качестве двухпортового регистрового файла БИС К1843ИР1

может выполнясь и ряд других функций. Так, при объединении управляющих

сигналов портов А и В можно получить модуль памяти с организацией

32 слова по 36 разрядов, с одним портом для записи и одним портом для чтения.

При этом на старшие разряды адресов чтения и записи порта А подается

высокий уровень, а на старшие разряды адресов чтения и записи порта В

— низкий уровень.

Для построения АЛУ, работающего в комплексной арифметике или ориентированного,

например, на выполнение элементарных операций быстрого преобразования Фурье,

из двух БИС может быть построен блок памяти с двумя портами для записи

и четырьмя портами для чтения. При этом соединяются параллельно

одноименные для обеих БИС выводы входных шин данных DA, DB,

адреса записи AWA, AWB и сигналы разрешения записи WEAC, WEAH, WEAL, WEBC, WEBH, WEBL.

![]()

Источники:

1. Микросхемы интегральные серии КС1590...КА1843.

- СПб.: Издательство РНИИ "Электронстандарт", 1993.

2. Титов М.А. и др. Изделия электронной техники. Микропроцессоры и однокристальные микроЭВМ: Справочник / М.А. Титов, А.Ю. Веревкин, В.И. Валерьянов; Под ред. А.И. Ладика и А.И. Сташкевича. - М.: Радио и связь, 1994.

3. Каталог. Цифровые и аналоговые интегральные микросхемы. Часть 2. Условные графические обозначения, назначения выводов и габаритные чертежи корпусов. - ГУП Центральное конструкторское бюро "Дейтон", 1998.

4. Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и их зарубежные аналоги.

Справочник, "НТЦ Микротех", 1998.

![]()