Крайне редкая серия. Информации по ней практически нет, известна только одна микросхема.

Производитель - "Экситон" (г.Павловский Посад)

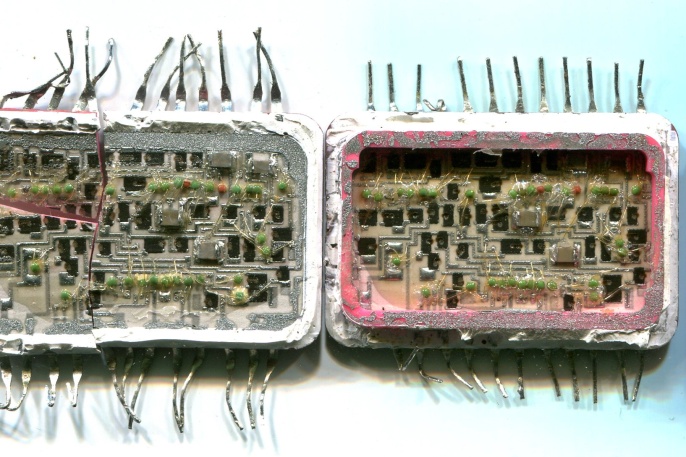

![]()

Микросборка для регистрации сигналов с пропорциональных камер.

Есть заводской паспорт от неё.

Схема содержит два канала со структурой "усилитель с высокоомным входным сопротивлением -

дискриминатор - одновибратор задержки - стробируемая память". Каналы имеют следующие

параметры: пopor срабатывания - 1,2 мB; врeмeннoe paзpeшeние, полученное с

пропорциональной камерой - 14 нс; номинальная задержка - 400 нс; мощность, потребляемая

каналом - 200 мВт. Микросборка имеет немагнитный корпус.

Разработка выполнена в Лаборатории высоких энергий Объединенного Института Ядерных Исследований (г.Дубна).

Усилитель имеет линейный вход для спектрометрии. Перед усилителем

возможно подключение встроенного каскада с общей базой, обладающего низким

входным сопротивлением.

Дискриминирующий одновибратор, кроме стандартизации переднего фронта импульса, служит

целям защиты одновибратора задержки от повторных входных сигналов (в интервале

задержки), поскольку его время выдержки в 1,5 раза больше, чем у одновибратора

задержки. Одновибраторы имеют вход регулировки времени выдержки внешним потенциалом,

кроме того, одновибратор задержки имеет вывод для точной подстройки с помощью

внешнего резистора. С одновибратора задержки снимается также сигнал 'Быстрое ИЛИ'.

Стробируемая схема памяти имеет входные сигналы управления в уровнях NIM, а выходной

сигнал — в уровнях TTL (открытый коллектор). Со схемы памяти также имеется выход ИЛИ.

|

высокоомный вход - 1,3 кОм; низкоомныи вход - 50 Ом | |

|

по линейному выходу - 15; по основному выходу - 300; по основному выходу с низкоомного входа - 300 мВ/мкА | |

|

| |

|

| |

|

|

|

номинальный - 1,2 мВ (tи = 60нс) минимальный - 0,5 мВ для положительных входных сигналов - не ниже 0,7 В | |

|

| |

|

время выдержки - в 1,5 раза больше длительности импульса одновибратора задержки. время восстановления - не более 15% от времени выдержки | |

|

| |

|

с изменением питания + 3В (Е1) - менее +0,3 мВ/В; - 3В (Е2) - менее +1,5 мВ/В; с изменением температуры - менее 0,5%°С |

|

номинально 400 нс, при Uynp = +3В диапазон регулирования - не менее +150 нс | |

|

с изменением питания + 3В (Е1) - менее +3%/В; - 3В (Е2) - менее -3%/В. с изменением температуры - -0,2%/°С |

|

| |

|

| |

|

записи - 15 нс, чтения - 40 нс, сброса - 20 нс | |

(фото с форума Портативное

ретрорадио)

Принципиальная схема одного канала :

Усилитель содержит транзистор смещения Т5. Каскад с ОБ реализован на транзисторе Т3, входное сопротивление его (50 Ом) обеспечено выбором величины режимного тока. Допустима непосредственная связь коллектора Т3 c входом усилителя. Усилитель имеет один внешний элемент - блокировочный конденсатор Cбл > 1 мкФ (возможна установка Cбл внутри ИС). Необходима также внешняя цепь защиты входа усилителя от пробоев ПК. Вывод для Cбл может быть использован также для регулировки порога срабатывания схемы, путем подачи в эту точку небольшого смещающего тока.

Дискриминирующий одновибратор (Т9 - Т13) и одновибратор задержки (Т14 - Т16) выполнены по классической схеме с эмиттерной связью, с диодом (D1, D2) для сокращения времени восстановления. Транзисторы Т12, Т16 и дополнительный источник смещения (Т17) ликвидируют зависимость времени выдержки от изменения напряжения питания Е2. Кроме защиты от повторных импульсов, дискриминирующий одновибратор защищает одновибратор задержки при перегрузках усилителя сигналами большой амплитуды. В этом случае на выходе усилителя импульс существенно удлиняется, что приводит к продлению импульса с дискриминирующего одновибратора. На выходе усилителя при перегрузках возможны также выбросы обратной полярности. Для предотвращения сокращения времени выдержки дискриминирующего одновибратора в этом случае включен транзистор Т10.

Сигнал с выхода одновибратора задержки дифференцируется (конденсатор 51 пф), передний фронт его используется в схеме "Быстрое ИЛИ" (Т18), а задний служит для записи в триггер памяти (Т21 - Т25) через ворота Т19, Т20. Режим схемы памяти и напряжение источника дополнительного смещения (транзистор Т29) выбраны таким образом, чтобы обеспечить слабое насыщение транзисторов в триггере и логические уровни, позволяющие работать по входам "Запись", "Чтение", "Сброс" с сигналами NIM . С памяти также имеется выход для организации сигнала ИЛИ (T24); сигнал чтения может быть снят в уровнях TTL.

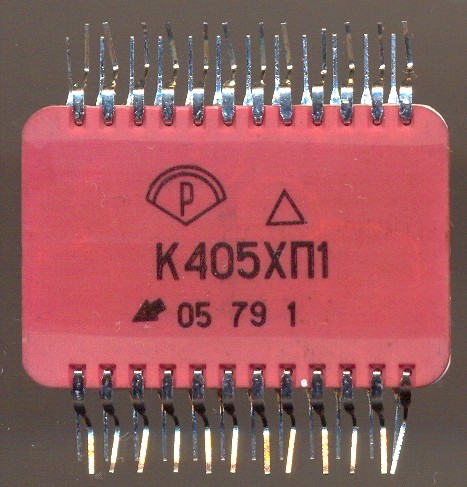

(фото Александра Назаренко)

![]()

Источники:

1. Ю.А.Афанасьев, С.Г.Басиладзе, М.В.Гусак,

C.M.Kopeненко, M.И.Mapкyc. Большая гибридная интегральная схема "Сдвоенный канал

регистрации для пропорциональных камер". - Объединенный Институт Ядерных Исследований,

Дубна, 1977.

2. С.Г. Басиладзе, В.К. Юдин. Электронная аппаратура

регистрации сигналов с пропорциональных камер на основе специализированной

интегральной схемы К405ХП1. - "Приборы и техника эксперимента" №4, 1979г.

3. А.В.Пиляр, А.А.Семенов, С.В.Сергеев, П.Стрмень,

А.А.Фещенко, В.Б.Флягин, Й.Шпалек. Система съема информации с пропорциональных камер

установки Гиперон на основе гибридной микросхемы К405ХП1. - Сообщения Объединенного

Института Ядерных Исследований, Дубна, 1982.

![]()