Среди цифровых интегральных схем

на модифицированной транзисторной логике с

непосредственными связями (МТЛНС, по

современной отечественной терминологии -

резисторно-транзисторная логика, РТЛ)

наибольшее распространение получили в

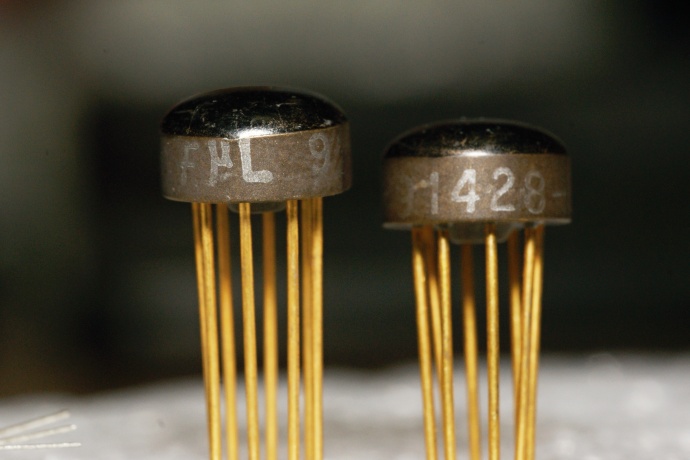

1962-1964 гг. микросхемы фирмы Fairchild Semiconductor

серий «милливаттная микрологика» (MWuL) и «быстродействующая

микрологика» (uL).

Эти две группы стандартных

схем, дополняющие друг друга по своим

характеристикам, насчитывали около 20 типов

интегральных схем и выпускались несколько

лет в больших количествах.

Эти две группы стандартных

схем, дополняющие друг друга по своим

характеристикам, насчитывали около 20 типов

интегральных схем и выпускались несколько

лет в больших количествах.

Сочетание двух групп микрологики позволяло удовлетворить

требования большого быстродействия или малой потребляемой мощности. Каждый тип

интегральной схемы имел свою матрицу интегральных компонентов, использующую

эпитаксиальный способ изоляции.

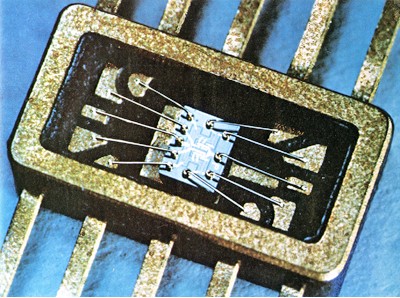

Все схемы являлись полупроводниковыми монолитными интегральными схемами.

Под торговой маркой µLogic (Микрологика) первая микросхема-триггер была предъявлена публике в марте 1961 на пресс-конференции на IRE Show в Нью-Йорке и на фотографии в журнале LIFE.

Еще пять микросхем, были введены в октябре. - Computer History Museum.

|

Один инвертор быстродействующей микрологики (uL) при средней рассеиваемой мощности 12 мвт может возбудить 5 uL инверторов или 16 MWuL инверторов, и имеет задержку распространения 12 нсек. Один инвертор милливаттной микрологики (MWuL) при средней рассеиваемой мощности 2 мвт может возбудить четыре других MWuL инвертора или один uL инвертор и один MWuL инвертор, и имеет задержку распространения около 45 нсек. Существенной особенностью схем МТЛНС является отсутствие в них конденсаторов. В тех случаях, когда необходимо создание импульсных схем мультивибраторов или одновибраторов, используются клапанные и триггерные интегральные схемы и внешние дискретные конденсаторы и резисторы, определяющие величину временной задержки. |

(фото Andrew Wylie / images courtesy of Andrew Wylie) |

Технические данные интегральных схем

| Модель | Выполняемая функция | Задержка распространения, нс | Рассеиваемая мощность, мВт | Примечание |

| uL903 | Трехвходовый клапан НЕ-И/НЕ-ИЛИ | 12 | 12 | |

| uL907 | Четырехвходовый клапан НЕ-И/НЕ-ИЛИ | 12 | 12 | |

| uL914 | Двойной двухвходовый клапан НЕ-И/НЕ-ИЛИ | 12 | 24 | |

| uL915 | Двойной трехвходовый клапан НЕ-И/НЕ-ИЛИ | 12 | 24 | |

| MWuL910 | Двойной двухвходовый клапан НЕ-И/НЕ-ИЛИ | 40 | 4 | |

| MWuL911 | Четырехвходовый клапан с инвертором НЕ-И, И/НЕ-ИЛИ, ИЛИ | 40, 80 | 4 | Клапан имеет 2 выхода |

| uL904 | Двухуровневый клапан И/ИЛИ, пригодный для использования в качестве законченного полусумматора | 16 | 34 | Клапан имеет 4 входа и 2 выхода |

| MWuL908 | Сумматор по модулю 2, клапан "исключающее ИЛИ" | 90 | 10 | Клапан имеет 4 входа и 2 выхода |

| MWuL912 | Двухуровневый клапан И/ИЛИ, пригодный для использования в качестве законченного полусумматора | 90 | 8 | Клапан имеет 4 входа и 2 выхода |

| uL900 | Инвертирующая буферная низкоимпедансная схема возбуждения | 16 | 30 | |

| MWuL909 | Двухвходовая клапанная инвертирующая буферная схема возбуждения | 80 | 10 | |

| uL902 | R-S триггер. Работает от положительных сигналов на входах S или R и CP | 14 | 22 | |

| uL905 | Клапанный R-S триггер c инвертором. Работает от отрицательных сигналов на входах S или R и CP | 18 | 53 | Имеет выход инвертированного стробирующего сигнала |

| uL906 | Клапанный R-S триггер. Работает от отрицательных сигналов на входах S или R и СР | 22 | 36 | |

| uL923 | J-K триггер. | Частота синхронизации до 2 МГц | ||

| uL916 | J-K триггер. Работает от отрицательных сигналов на входах J, K, CP или положительного сигнала на входе PS | Частота синхронизации до 10 МГц | 52 | |

| uL926 | J-K триггер. Работает от отрицательных сигналов на входах J, K, CP или положительного сигнала на входах CL или PS | Частота синхронизации до 20 МГц | 56 | |

| MWuL913 | Триггер D-типа. Работает от отрицательных и положительных сигналов на входе D и от отрицательного сигнала на входе СР | 100 | 15 | |

| uL901 | Дополнительная схема для счетчика | 24 | 55 | |

| MWuL921 | Двойной двухвходовый расширитель клапанов НЕ-И/НЕ-ИЛИ | - | - |

![]()

Входные, передаточные и выходные характеристики клапанов этих двух групп показаны на рисунке для нормальных внешних условий и разветвления на выходе, равного 1. На этом же рисунке показаны схемы клапанов и величины сопротивлений коллекторных и базовых резисторов схем быстродействующей микрологики и милливаттной микрологики.

а – входные характеристики; б – передаточные характеристики; в – выходные характеристики; г – принципиальные схемы клапанов

![]()

Буферный каскад типа 900 представляет собой инвертирующий промежуточный преобразователь с малым импедансом. Время распространения сигнала 16 нсек, выделяемая мощность 30

мВт при 25° С, коэффициент разветвления по выходу 25.![]()

![]()

Триггер типа 902 служит в качестве двоичной ячейки памяти. Время срабатывания 14 нсек, рассеиваемая мощность 22

мВт при 25° С, коэффициент разветвления по выходу 4.![]()

![]()

Трехвходовый вентиль типа 903 выполняет логические операции НЕ—И/НЕ—ИЛИ. Время распространения сигнала 12 нсек, рассеиваемая мощность 12

мВт при 25° С, коэффициент разветвления по выходу 5.

![]()

![]()

Полусумматор типа 904, представляющий собой двухуровневую схему И/ИЛИ, может служить в качестве готовой ячейки полусумматора, а также вентиля, выполняющего логические функции типа «исключающее ИЛИ» и ряд других. Время распространения импульса 18 нсек, рассеиваемая мощность 34

мВт при 25° С, коэффициент разветвления по выходу 5.

![]()

![]()

Вентиль типа 907 на четыре входа представляет собой схему НЕ—И/НЕ—ИЛИ с четырьмя входами. Время распространения сигнала 12 нсек, рассеиваемая мощность 12

мВт при 25° С, коэффициент разветвления по выходу

5.

![]()

![]()

Сумматор типа 908 выполняет

операцию сложения в двоичной системе и

операцию "исключающее ИЛИ". Время

срабатывания 90 нсек, рассеиваемая мощность

10 мВт при 25°С, коэффициент разветвления по

выходу 4.![]()

![]()

Элемент типа 909 представляет собой инвертирующий возбудитель с малым входным импедансом. Типичными схемами применения являются возбудители, мультивибраторы, а также схемы дифференцирования импульсов. Время распространения сигнала 80 нсек, рассеиваемая мощность 10 мВт при 25 °С, коэффициент разветвления по выходу 30.

![]()

Двойной вентиль типа 910 может быть использован как два логических вентиля НЕ — ИЛИ, триггер с раздельными входами установки и сброса, сдвоенный инвертор или как два раздельных инвертора. Время срабатывания 45 нсек, рассеиваемая мощность 4

мВт при 25° С, коэффициент разветвления по выходу 4.![]()

![]()

Вентиль типа 911 на четыре входа может служить в качестве схемы ИЛИ. Время срабатывания 80 нсек, рассеиваемая мощность 4

мВт при 25° С, коэффициент разветвления по выходу 4.![]()

![]()

|

|

Двойной вентиль типа 914 на два входа представляет собой двойную схему НЕ—И/НЕ—ИЛИ и может служить для построения триггеров, неинвертирующих вентилей или комбинации вентиля с инвертором. Время распространения сигнала 12 нсек, рассеиваемая мощность 24

мВт при 25° С, коэффициент разветвления по выходу 5.

![]()

![]()

Возле входных и выходных выводов указаны нагрузочные коэффициенты. У схем uL в скобках указаны нагрузочные коэффициенты, соответствующие MWuL.

Двойной вентиль типа 915 на три входа представляет собой комбинацию из двух трехвходовых схем НЕ—И/НЕ—ИЛИ.

Выпускаются три близкие по конструкции разновидности вентиля.

Время распространения сигнала 12 нсек, рассеиваемая мощность 24 мВт при 25°С,

коэффициент разветвления по выходу 5.

![]()

![]()

J—К триггер типа 916 — готовый универсальный элемент памяти, пригодный для применения в регистрах сдвига, счетчиках или для выполнения различных операций управления. Время срабатывания 10 нсек, рассеиваемая мощность 52 мВт при 25°С, коэффициент разветвления по выходу 3.

Необходимо отметить, что в этих триггерах временное запоминание информации осуществляется с помощью транзисторов с накоплением заряда. В нормальном состоянии на вход СР подается положительный сигнал строба, который инвертируется транзистором Т4, так что на его коллекторе и на соединенных с ним коллекторах транзисторов Т8 и Т9, накапливающих заряд, появляется низкий уровень напряжения.

В результате этого выключаются транзисторы Т3 и Т6, входящие в состав входных клапанов на транзисторах Т1, Т2, Т3 и Т5, Т6, Т7. Кроме того, в схеме существует перекрестная связь с выходных транзисторов триггера Т11 и Т12 на базы транзисторов Т6 и Т2, благодаря которой один из этих транзисторов выключен, а другой включен. Этим блокируется один из клапанов НЕ-И.

Если теперь на входы J или К или J и К также подан отрицательный сигнал с выхода цифровой логической цепи, то на всех трех входах одного из клапанов НЕ-И могут оказаться низкие уровни напряжения, и на выходе этого клапана, на коллекторах транзисторов Т1, Т2, Т3 или Т5, Т6, Т7 появится высокий уровень напряжения. В результате через резистор R8 и базово-коллекторный переход транзистора Т8 или резистор R10 и базово-коллекторный переход транзистора Т9 потечет ток в коллектор транзистора Т4. Проходя в прямом направлении через базово-коллекторный переход транзистора Т8 или Т9, этот ток будет вызывать в нем накопление заряда.

Через некоторое время после подачи сигнала на входы триггера J и К, на вход СР подается отрицательный стробирующий сигнал, выключающий транзистор Т4, через который протекал ток из резистора R15. В результате ток из резистора R15 теперь будет проходить через коллектор одного из транзисторов T8 или Т9, в котором имеется накопленный заряд, и подаваться в базу одного из выключенных выходных транзисторов Т11 или T12. Это приведет к включению соответствующего транзистора и вызовет переброс триггера в противоположное состояние. Помимо этого ток из резистора R15 будет также проходить в базы транзисторов Т3 и Т5, которые через некоторое время окажутся включенными, блокируя входные клапаны НЕ-И и препятствуя ложному срабатыванию триггера во время этого же стробирующего импульса.

Поскольку включение транзисторов Т3 и Т5 несколько задерживается, то на базе транзистора Т8 или Т9 существует положительный потенциал, и транзистор некоторое время действует как эмиттерный повторитель. Дополнительная задержка включения транзисторов Т3 и Т5 достигается благодаря резистору R9, включенному в цепь их баз. Выходные уровни триггера задерживаются относительно отрицательного фронта стробирующего сигнала: на 18 нсек отрицательный и на 40 нсек положительный уровень.

Наличие в схеме транзистора Т4, инвертирующего входной стробирующий сигнал, обеспечивает усиление и улучшение формы входного стробирующего сигнала и восстановление длительности его отрицательного фронта. В результате длительность отрицательного фронта стробирующего сигнала может составлять от 1 до 100 нсек. Для нормальной работы триггера логические сигналы, подаваемые на входы J и К, не должны изменяться в течение 25 нсек до и после прихода отрицательного стробирующего импульса, минимальная ширина которого составляет 50 нсек.

J-K триггер uL916 может работать в диапазоне температур от —55 до +125° С, обеспечивая в наихудшем случае получение частоты синхронизации 8

МГц.![]()

![]()

Каскад типа 921 представляет собой двойной вентиль на два входа без активных сопротивлений в узлах. Время прохождения сигнала через каскад 40 нсек.![]()

![]()

uL923 - J-K триггер. Может работать с тактовой частотой до 2 МГц; допустимая ёмкость нагрузки до 5 пФ. Справочный лист на него.

![]()

Источники:

1. Курносов А.И., Воронков Э.Н. Полупроводниковая микроэлектроника. М., Воениздат, 1973.

![]()