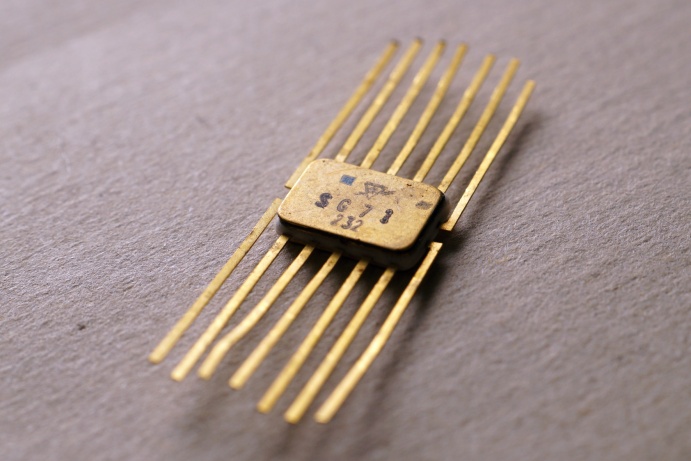

Примером цифровых интегральных схем транзисторно-транзисторной логики являлись цифровые интегральные схемы серии универсальная высокоуровневая логика (SUHLI, Sylvania Universal High-level Logic - I) фирмы Sylvania (США). Это первая коммерчески успешная ТТЛ серия, ставшая таковой благодаря военным заказам (в первую очередь, применению в ракете "воздух-воздух" AIM-54).

![]()

Технические данные этих схем:

| Модель | Выполняемая функция | Задержка распространения, нсек | Рассеиваемая мощность, мвт |

| SG-40 | Двойной четырехвходовый клапан НЕ-И/НЕ-ИЛИ | 10 | 30 |

| SG-50 | Расширяемый тройной двухвходовый и трехвходовый клапан ИЛИ | 12 | 35 |

| SG-60 | Восьмивходовый клапан НЕ-И/НЕ-ИЛИ | 12 | 15 |

| SG-90 | Клапан «исключающее ИЛИ» с дополняющим выходом | 12 (выход

K) 24 (выход L) |

35 |

| SG-100 | Расширяемый тройной трехвходовый клапан ИЛИ | 12 | 25 |

| SG-110 | Расширяемый двойной четырехвходовый клапан ИЛИ | 12 | 20 |

| SG-120 | Расширяемый восьмивходовый клапан НЕ-И/НЕ-ИЛИ | 18 | 15 |

| SG-130 | Возбудитель линии, клапан НЕ-И/НЕ-ИЛИ | 25 | 60 |

| SG-140 | Четверной двухвходовый клапан НЕ-И/НЕ-ИЛИ | 10 | 60 |

| SG-150 | Двойной двухвходовый и двойной трехвходовый расширитель для клапанов ИЛИ | 4 | 20 |

| SG-160 | Тройной двухвходовый возбудитель | 15 | 45 |

| SG-170 | Двойной четырехвходовый расширитель для клапанов ИЛИ | 3 | 10 |

| SG-180 | Двойной четырехвходовый расширитель для клапанов НЕ-И/НЕ-ИЛИ | - | - |

| SG-190 | Тройной трехвходовый клапан НЕ-И/НЕ-ИЛИ | 10 | 45 |

| SF-10 | R-S триггер | 24 | 30 |

| SF-20 | Двухфазный стробируемый R-S триггер | 24 | 30 |

| SF-30 | Однофазный R-S-T триггер | 24 | 30 |

| SF-50 | J-K триггер (входы И) | частота синхронизации до 20 МГц | 50 |

| SF-60 | J-K триггер (входы ИЛИ) | 55 |

![]()

Типичный двойной клапан этой серии SG-40 имеет величину сопротивлений резисторов: R1 = R2 = 4 ком; R3 = R4 = R7 = R8 = 1 ком и R5 = R6 = 120 ом

:

![]()

|

Схемы ТТЛ серии универсальной высокоуровневой логики фирмы Sylvania имеют разветвление на выходе, доходящее до 15 при скорости переключения, почти достигающей 10 нсек, и средней рассеиваемой мощности на один клапан, равной 15 мвт. Запас от помех у них при 25°С составляет около 1 в. Все схемы являются монолитными цифровыми интегральными схемами и используют однократную эпитаксию и диффузионный утопленный слой. Высокое быстродействие достигается благодаря малым геометрическим размерам компонентов, получаемым в результате применения фоторезистивных процессов с очень высокой разрешающей способностью. Интегральные схемы используют плоский корпус из твердого стекла с 14 выводами, имеющий размеры 6,35x4,45 мм. |

(фото Andrew Wylie / images courtesy of Andrew Wylie) |

В семейство ТТЛ этой серии входили 19 типов цифровых интегральных схем, включающих многофункциональные цифровые интегральные схемы и разнообразные триггерные интегральные схемы, в том числе и схемы J-K триггеров. Все эти схемы принципиально похожи на схемы обычной диодно-транзисторной логики. Исключение составляет цифровая интегральная схема J-K триггера SF-50, обеспечивающая работу при частоте запуска до 20 Мгц и аналогичная ей схема J-K триггера SF-60.

![]()

|

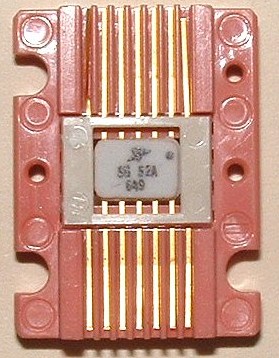

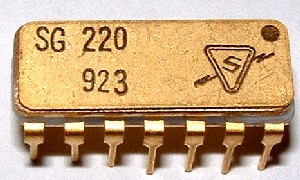

В 1965 году фирма Sylvania приступила к выпуску второй модификации интегральных схем ТТЛ серии универсальной высокоуровневой логики (SUHLII), в число первых интегральных схем которой входят 9 интегральных схем клапанов и 8 интегральных схем J-K триггеров. Они включают интегральные схемы клапанов И/ИЛИ и интегральные схемы двойных J-K триггеров: |

(фото Andrew Wylie / images courtesy of Andrew Wylie) |

| Модель | Выполняемая функция | Задержка распространения, нсек | Рассеиваемая мощность, мвт |

| SG-210 | Расширяемый двойной четырехвходовый клапан ИЛИ | 7 | 30 |

| SG-220 | Четверной двухвходовый клапан НЕ-И/НЕ-ИЛИ | 6 | 88 |

| SG-230 | Двойной двухвходовый и двойной трехвходовый расширитель для клапанов ИЛИ | 2 | 30 |

| SG-240 | Двойной четырехвходовый клапан НЕ-И/НЕ-ИЛИ | 6 | 44 |

| SG-250 | Расширяемый тройной двухвходовый и трехвходовый клапан ИЛИ | 7 | 45 |

| SG-260 | Восьмивходовый клапан НЕ-И/НЕ-ИЛИ | 8 | 22 |

| SG-270 | Двойной четырехвходовый расширитель для клапанов ИЛИ | 2 | 15 |

| SF-250 | J-K триггер (входы И) | частота синхронизации до 30 МГц | 60 |

| SF-260 | J-K триггер (входы ИЛИ) | 60 | |

| SG-280 | Двойной четырехвходовый клапан И/ИЛИ | 10 | 76 |

| SG-290 | Двойной двух- и трехвходовый расширитель | 10 | 76 |

![]()

Основное отличие этой новой серии интегральных схем заключается в том, что за счет некоторого повышения рассеиваемой мощности (с 15 до 22 мвт) в каждой отдельной схеме клапана было достигнуто существенное увеличение быстродействия. Задержка распространения у клапанов ТТЛ серии SUHLII составляет уже только 6 нсек, а максимальная частота синхронизации у триггеров ТТЛ серии SUHLII достигает 50 Мгц. Обладая в то же время высоким запасом от помех (более 1 в при 25° С), большим разветвлением на выходе (до 12) и большим логическим перепадом выходных сигналов (уровень напряжения логического «0» равен 0,25 в, уровень напряжения логической «1» равен 3,5 В), интегральные схемы ТТЛ второй модификации серии универсальной высокоуровневой логики фирмы Sylvania являлись одними из наиболее быстродействующих среди известных в то время интегральных схем и позволяли создавать сложные быстродействующие цифровые системы, имеющие большой запас от помех и сравнительно небольшую рассеиваемую мощность.

![]()

Источники:

1. Курносов А.И., Воронков Э.Н. Полупроводниковая микроэлектроника. М., Воениздат, 1973.

![]()